# Processing parameters of PCBs manufactured by TS PCB Techno-Service S.A.

## Table of contents

| 1. | Proces  | ssing parameters of PCB materials     | 3   |

|----|---------|---------------------------------------|-----|

|    | 1.1.    | Applied laminate types                | . 3 |

|    | 1.2.    | Finished PCB thickness tolerance      | 3   |

|    | 1.3.    | Multilayer PCB base materials         | . 3 |

|    | 1.4.    | Special laminate parameters           | 4   |

|    | 1.5.    | Masks and silkscreen layers           | . 4 |

|    | 1.6.    | Types of finish                       | . 5 |

| 2. | PCB (C  | NC) machining                         | 5   |

|    | 2.1.    | Drilling                              | . 5 |

|    | 2.2.    | Routing/milling                       | . 6 |

|    | 2.3.    | Scoring                               | . 6 |

|    | 2.4.    | Chamfering                            | . 7 |

|    | 2.5.    | Z-routing                             | . 7 |

|    | 2.6.    | PCB panelization                      | . 7 |

| 3. | Vias    |                                       | 7   |

|    | 3.1.    | Via type                              | 7   |

|    | 3.2.    | Via finish                            | . 8 |

| 4. | DRC cr  | ritical parameters of mosaics         | 8   |

|    | 4.1.    | Minimum length and thickness of paths | . 8 |

|    | 4.2.    | Minimum ring sizes and hole spacing   | 9   |

|    | 4.3.    | Aluminium based PCBs                  | . 9 |

| 5. | PCB m   | arking                                | 10  |

|    | 5.1.    | UL non-flammability certification     | 10  |

|    | 5.2.    | Date stamping                         | 10  |

|    | 5.3.    | Other markings                        | 10  |

| 6. | List of | abbreviations and symbols             | 10  |

## 1. Processing parameters of PCB materials

We manufacture the following PCB types:

- Single-sided PCBs on: FR4 laminates (NPTH), aluminium laminates (no hole plating available), and Rogers (no hole plating available);

- Double-sided PCBs on: FR4 (PTH / NPTH), aluminium laminates (NPTH), microwave Rogers (PTH/ NPTH, depending on the specific laminate type applied);

- Multilayer PCBs, with up to 8 layers on FR4 (PTH / NPTH).

## 1.1. Applied laminate types

The processing parameters of the typical laminates used in PCB production are shown in Table 1. We manufacture PCBs in the laminate thickness range of **0.2-3.2 mm**. We always carry the following FR4 laminate thickness series [mm] in stock: **0.2**; **0.36**; **0.5**; **0.6**; **0.71**; **0.8**; **1.0**; **1.2**; **1.55**; **2.0**; **2.4**; **3.2**.

| Laminate type /<br>designation                   | Laminate thickness<br>[mm]                  | Base Cu thickness [µm] | Tg <sup>*</sup> [°C] | СТІ <sup>*</sup> [V] |  |

|--------------------------------------------------|---------------------------------------------|------------------------|----------------------|----------------------|--|

| FR4                                              | 0.2-3.2                                     | 18-105                 | 130                  | 175-249 (PLC3)       |  |

| Aluminium (2 W/mK)                               | 1.0-3.2                                     | 35, 70, 105            | N/A                  | >600 (PLC0)          |  |

| Rogers: RO4000, RO3000,<br>RT/duroid®5870 / 5880 | Selected accordingly for<br>custom projects | 18, 35, 70             | N/A                  | N/A                  |  |

Table 1. Basic laminate parameters

\* Laminates with a higher Tg and or CTI available on custom orders.

### 1.2. Finished PCB thickness tolerance

The list of thickness limits for finished single- and double-sided FR4-based PCBs (i.e. total PCB thickness values) is shown in Table 2.

| Base<br>laminate<br>thickness | Base Cu<br>thickness<br>[mm] | permissible<br>range | ed PCB<br>e thickness<br>[mm] |  |

|-------------------------------|------------------------------|----------------------|-------------------------------|--|

| [mm]                          |                              | min.                 | max.                          |  |

|                               | 18 µm                        | 0.38                 | 0.43                          |  |

| 0.2                           | 35 µm                        | 0.42                 | 0.47                          |  |

|                               | 70 µm                        | 0.49                 | 0.54                          |  |

|                               | 18 µm                        | 0.53                 | 0.60                          |  |

| 0.36                          | 35 µm                        | 0.56                 | 0.64                          |  |

|                               | 70 µm                        | 0.63                 | 0.71                          |  |

|                               | 0.018                        | 0.87                 | 0.97                          |  |

| 0.71                          | 0.035                        | 0.90                 | 1.00                          |  |

| 0.71                          | 0.07                         | 0.97                 | 1.07                          |  |

|                               | 0.105                        | 1.04                 | 1.14                          |  |

#### Table 2. Laminate thickness tolerance

| Base<br>laminate<br>thickness<br>[mm] | Base Cu<br>thickness<br>[mm] | Finishe<br>permissible<br>range<br>min. | thickness |  |

|---------------------------------------|------------------------------|-----------------------------------------|-----------|--|

| 0.51                                  | 0.018                        | 0.67                                    | 0.77      |  |

| 0.60                                  | 0.018                        | 0.76                                    | 0.86      |  |

| 0.80                                  | 0.018                        | 0.93                                    | 1.08      |  |

| 1.00                                  |                              | 1.10                                    | 1.25      |  |

| 1.20                                  | _                            | 1.30                                    | 1.45      |  |

| 1.40                                  | Cu                           | 1.50                                    | 1.65      |  |

| 1.55                                  | thickness<br>in base         | 1.65                                    | 1.80      |  |

| 2.00                                  | laminate                     | 2.07                                    | 2.27      |  |

| 2.40                                  | ianniate -                   | 2.47                                    | 2.67      |  |

| 3.20                                  |                              | 3.24                                    | 3.50      |  |

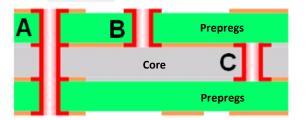

### 1.3. Multilayer PCB base materials

The typical materials we use in multilayer PCB production are shown in Table 3. The typical Tg value is **130°C** and the CTI may reach **249 V**. We also offer laminates with higher Tg and CTI values.

| Material type | Thickness [mm]                                                           | Comments                                                                                                                                   |

|---------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Core          | 0.10; 0.20; 0.36;                                                        | The maximum permissible thickness of a usable core is 2.8 mm.                                                                              |

|               | 0.50; 0.71; 1.00                                                         |                                                                                                                                            |

| Prepreg       | Type 106: 0.045<br>Type 1080: 0.06<br>Type 2125: 0.09<br>Type 7628: 0.18 | The minimum number of interlayer prepregs is 2. Hence the lowest spacing between two adjacent layers is ca. 0.1 mm (2 x pregreg type 106). |

| Copper foil   | 0.018; 0.035; 0.070                                                      | Applied as outer conductive layers.                                                                                                        |

Table 3. Parameters of typical multilayer PCB materials

The PCBs of this type can have the following Cu layer thicknesses:

- Outer layers (finished) [μm]: 35; 70; 105; 140; 170; 210; 240;

- Inner layers [μm]: 18; 35; 70; 105.

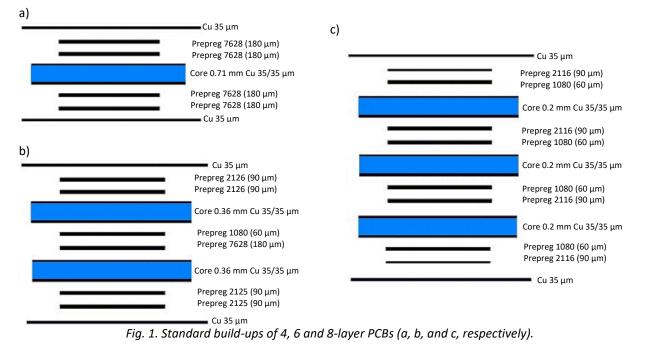

The standard build-ups of multilayer PCBs are shown in Fig. 1. The figure presents the cross-sections of stacks, the parameters of applied cores and prepregs, and the finished Cu foil thickness values for specific conductive layers.

Aside from the standardised solutions, we offer custom stack-ups with customer-specific types and thickness values of individual components.

### 1.4. Special laminate parameters

We also provide laminates with non-standard parameters. We carry certain special laminates in stock at all times, while some models must be ordered according to customer-specific requirements. The following shows example parameters of non-standard laminates:

- Tg: 150°C, 180°C;

- CTI: PLC0 ≥ 600 V;

- Finished Cu thickness: 240 μm max.;

- Halogen-free laminates;

- Aluminium laminates with TC > 2 W/mK (5 W/mK max.);

- Non-anodised aluminium laminates

### 1.5. Masks and silkscreen layers

#### Soldermasks

Our soldermasks are based on the **Peters SD24XX** series. Our range of soldermask colours and gloss levels is shown below:

- Green: semi-matt (standard) or gloss;

- White semi-matt:

- Blue: semi-matt:

- Red: semi-matt:;

- Black: semi-matt or extra-matt;

- Yellow: semi-gloss.

#### Peelable mask

We use **Peters SD2955** peelable masks for coating the PTHs with maximum diameters to **1.9 mm**. The peelable masks are deposited on one or both sides of the finished PCB. The average deposited peelable mask thickness is ca. **0.3 mm**.

#### Silkscreen layers

The text layers are screen-printed with **Peters SD24XX** series inks. The minimum text line thickness is **4 mils (ca. 0.1 mm)**. All text parts that overlap with soldermask pads or beyond the PCB's outline are always cut off. We print legend layers in white (standard), blue, red, black and yellow.

#### 1.6. Types of finish

Exposed copper pads can be finished in three available variants, shown in Table 4. Note that the coating is deposited on the naked Cu areas without the resists.

| Туре    | Synonym             | Coat thickness    | Comments                                                                |  |  |  |

|---------|---------------------|-------------------|-------------------------------------------------------------------------|--|--|--|

| HAL     | Pb-free HAL, HASL,  | 1 μm – 40 μm      | The coating surface is never perfectly flat, and no specific exact      |  |  |  |

| Pb free | Pb-free tin plating |                   | thickness is manufacturable.                                            |  |  |  |

| ENIG    | Chemical            | Gold layer:       | Required whenever:                                                      |  |  |  |

|         | immersion gold      | 0.04 μm – 0.12 μm | <ul> <li>The base laminate thickness is below 0.36 mm;</li> </ul>       |  |  |  |

|         | plating             | Nickel layer:     | <ul> <li>BGA/µBGA circuits are present;</li> </ul>                      |  |  |  |

|         |                     | 4.0 μm – 6.0 μm   | <ul> <li>Blind/buried vias are present;</li> </ul>                      |  |  |  |

|         |                     |                   | -4 mils spacing are present (between exposed copper                     |  |  |  |

|         |                     |                   | elements);                                                              |  |  |  |

|         |                     |                   | - Single-sided SMD is present, and the minimum distan                   |  |  |  |

|         |                     |                   | between the pad edges is 8 mils or less;                                |  |  |  |

|         |                     |                   | - Double-sided SMD is present, and the minimum distance                 |  |  |  |

|         |                     |                   | between the pad edges is 11.8 mils or less;                             |  |  |  |

|         |                     |                   | – The laminate thickness is $\geq$ 1.55 mm and plated slots are also    |  |  |  |

|         |                     |                   | present;                                                                |  |  |  |

|         |                     |                   | <ul> <li>Half-holes and half-slots are present on the edges.</li> </ul> |  |  |  |

|         |                     |                   | Recommended whenever:                                                   |  |  |  |

|         |                     |                   | <ul> <li>Plated edges or plated slots are present.</li> </ul>           |  |  |  |

| Non-    | -                   | -                 | The copper has no protective layer deposited and becomes matt           |  |  |  |

| coated  |                     |                   | by oxidation.                                                           |  |  |  |

## Table 4. Available pad coating

## 2. PCB (CNC) machining

#### 2.1. Drilling

Drilling is the process for the production of PTHs, semi-PTHs and NPTHs of up to 6 mm in diameter. Larger holes are milled. Basic drilling parameters:

| <ul> <li>Min. drill diameter:</li> </ul>       |                                             | 0.25 mm             |

|------------------------------------------------|---------------------------------------------|---------------------|

| <ul> <li>Min. via diameter:</li> </ul>         |                                             | 0.15 mm             |

| <ul> <li>Max. buried via diameter:</li> </ul>  |                                             | 1.5 mm              |

| <ul> <li>Standard PTH diameter tole</li> </ul> | rance:                                      | +0.1 mm / -0.05 mm  |

| <ul> <li>Standard NPTH diameter to</li> </ul>  | lerance:                                    | +0.1 mm / -0.05 mm  |

| - Standard plated slot dimens                  | sional tolerance:                           | .+0.1 mm / -0.05 mm |

| The maximum drilled hele a                     | liamator is 6 mm. Larger belos need milling |                     |

The maximum drilled hole diameter is 6 mm. Larger holes need milling.

Non-standard diameter tolerances are manufacturable (e.g. at  $\pm 0.05$  mm). This must be specified in the purchase order as the expected hole diameter tolerance value. Moreover, indicate which holes must be made to that tolerance.

## 2.2. Routing/milling

Routing/milling is applied to machine the edges of PCBs and panels, mill slots and cuts, make large holes (>6 mm), or mill panels with fixing tabs. Basic milling parameters:

| – Min. mill diameter:                                   | 0.6 mm                            |

|---------------------------------------------------------|-----------------------------------|

| - Standard mill diameter:                               | 2.0 mm                            |

| - Available mill diameters [mm]:                        | 0.6; 0.8; 1.0; 1.2; 1.5; 2.0; 2.4 |

| <ul> <li>Standard milling/routing tolerance:</li> </ul> | ±0.1 mm                           |

Milling/routing with tools less than 2 mm in diameter must always be specified in your purchase order, unless the design states the requirement explicitly. Note that non-standard milling, for instance using small diameter tools (below 1.5 mm), may significantly increase the cost. Non-standard milling/routing tolerances are manufacturable and must be specified in the purchase order. Also, specify the PCB dimensions to be processed to non-standard tolerance values (preferably on the design drawings).

## 2.3. Scoring

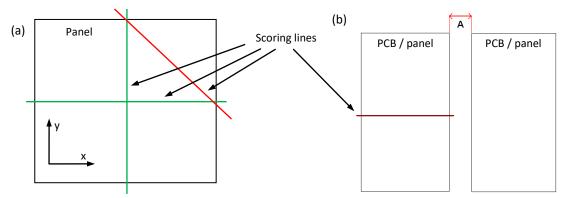

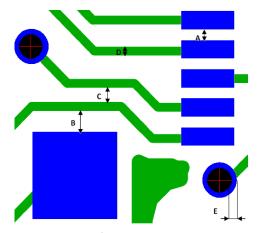

Scoring (also v-cutting) is a process of cutting the PCBs and panels for easy depanelization after automatic assembly. The v-cuts can be manufactured horizontally and vertically as well as using continuous or skipping lines. Fig. 2a shows the standard scoring lines in green. Diagonal scoring is not possible (see the red line).

Fig. 2. (a) Standard and non-permitted scoring lines, and (b) PCB layout for skipping v-cutting.

Fig. 2b shows an example of skipping, where the scoring line is intermittent along its length. Here the non-scored spacing between adjacent PCBs (Fig. 2b dimension A) must be 10 mm or wider to prevent damage to the adjacent non-scored PCB.

Basic scoring parameters:

| - Lowest laminate thickness for scoring: |  | 0.36 mm |

|------------------------------------------|--|---------|

|------------------------------------------|--|---------|

– Single-sided scoring: For laminates ≥ 0.50 mm thick

- Scoring line tolerance:  $\pm$ 0.1 mm

The minimum non-scored part of single-sided scored laminates is 0.15 mm. This applies to laminates in the range of  $\geq$ 0.5 mm to <0.8 mm. 0.3 mm of non-scored laminate is left by default in the laminate thickness range of 0.8 mm to <2.4 mm. The non-scored portion of 2.4mm or thicker laminates is 20% of the thickness.

The minimum permissible distance of mosaic details from scoring lines is shown in Table 5.

| FR4 laminate thickness<br>[mm] | 0.55 | 0.80 | 1.00 | 1.20 | 1.55 | 2.00 | 2.40 |

|--------------------------------|------|------|------|------|------|------|------|

| Minimum spacing [mm]           | 0.15 | 0.21 | 0.26 | 0.31 | 0.4  | 0.52 | 0.62 |

## 2.4. Chamfering

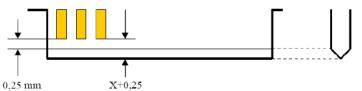

Chamfering is canting the PCB edge on both sides; this is usually done at the edge joint to facilitate the assembly of the pin raster in the socket (see Fig. 3). The process can be handled in two ways:

- Standard chamfering, performed along the entire PCB edge (with a special machine). If PCBs are to be

depanelized, the chamfered edge must be oriented outwards and not blocked by the margin.

- Skipping, performed if the edges to be chamfered are within the panel (i.e. the edge to be processed is not accessible from the outside). Chamfering is done by routing, and the minimum permissible PCB spacing must be as in skip milling (see Fig. 2b).

Basic chamfering parameters:

- Standard chamfer angle: 45°

- Laminate thickness 1.55 mm and chamber at 45°: ..... X=0.675 mm (see Fig. 2)

- Laminate thickness 1.55 mm and chamber at 30°: ..... X=1.170 mm (see Fig. 2)

Fig. 3. Preparing an edge joint raster for chamfering

## 2.5. Z-routing

Z-routing is done on FR4 laminates and consists in milling a specific outline to a defined depth (i.e. deduction of the laminate mass in the Z axis). The operation can be done on either or both sides of the PCB. The standard z-routing mill diameter is **2 mm**.

Note that z-routing is more labour consuming than standard milling. If larger areas of a PCB are to be z-routed, consult the processing method to be used before placing your purchase order.

## 2.6. PCB panelization

Large series PCBs intended for automatic assembly are composed in panels (multi blocks). It is common to leave a laminate strip (the margin) along the panel's long side as a holding mount clearance for automatic assemblers.

PCBs are also manufactured in panels if one of the PCB sides is less than **30 mm** long. Techno-Service composes the PCBs in panels according to its process, unless a panelised PCB design is provided. Specific panel types exist depending on their machining processes:

- a) **Scored board**, recommended for rectangular PCBs, especially on aluminium laminates. The PCBs are butted together in panels with a **6 mm** wide margin along the panels' longer sides.

- b) Non-perforated routed panel with fixing tabs. Here the PCBs are composed at a spacing of 2 mm with the fixing tabs spaced at 50 mm and a 7 mm wide margin.

- c) Perforated routed panel with fixing tabs. Here the PCBs are panelized at a spacing of 2 mm with the fixing tabs spaced at 50 mm and a 7 mm wide margin. The fixing tabs feature additional perforated holes for easier breaking of the PCBs from the panel.

- d) **Mixed panel**. This type combines the properties of scored and routed panels.

## 3. Vias

## 3.1. Via types

We manufacture three types of plated vias, as shown in Fig. 3. **Standard vias** (see Fig. 4 detail A) are made in double-sided and multilayer PCBs. The vias enable electric connections between the top and bottom mosaics and between the inner layers, since they pass through the entire PCB thickness. The minimum via diameter is **0.15 mm** (as finished).

TECHNO-SERVICE S.A.

Fig. 4. Cross-section of a PCB with via types shown: A — Standard, B – Blind, C – Buried.

[mm];

- Blind via holes must be gold plated;

- Blind vias are manufacturable on one or both PCB sides.

**Buried vias** (see Fig. detail C) can only connect the conductive layers on both sides of multilayer PCB cores (i.e. the core inner layers, see example in Fig. 4). The blind via diameter is **1.5 mm** maximum, and the PCB must be gold plated.

## 3.2. Via finish

The following via finish variants are most often used in PCBs:

- Unmasked vias: this is the most popular solution. The via rings are finished with the coating chosen by the customer.

- Covered vias: the vias are coated with the soldermask and usually not plugged. The soldermask pours over into the vias to coat the hole edges and walls.

- Plugged vias: the vias are filled with a special heat cured ink. The process allows plugging vias in the diameter range of 0.3-1.0 mm.

- **Plugged and covered vias**: plugged vias which are additionally coated with the soldermask.

- Plugged and covered flat vias: the vias are mostly flat and with a fill level of > 80%. Here the PCBs must be goldplated. The process facilitates sealing holes up to 0.6 mm in diameter, including pad holes, but the plugging ink is not copper-coated and leaves a 3 mils wide ring around the hole's clearance.

## 4. DRC critical parameters of mosaics

### 4.1. Minimum length and thickness of paths

Fig. 5 highlights the typical PCB mosaic parameters that are subject to DRC for compliance with the specified Cu layer thickness.

Fig. 5. Legend of PCB mosaic element distance dimensions: A – pad/pad, B – pad/trace, C – trace/trace, D – path width, E – ring diameter. The minimum distance values between the PCB mosaic components and path width values depend on the Cu layer thickness. Table 6 shows the minimum permissible DRC values as a function of base Cu thickness, i.e. the thickness value of Cu prior to plating.

Table 6. Minimum distances and paths at Cu thickness

| Designation | Base Cu thickness [µm]  | 12 | 18 | 35 | 70 | 105 | 140 | 170 | 210 |

|-------------|-------------------------|----|----|----|----|-----|-----|-----|-----|

| Α           | Pad/Pad [mils]          | 3  | 4  | 5  | 9  | 12  | 15  | 19  | 27  |

| В           | Pad/Trace [mils]        | 3  | 4  | 5  | 9  | 12  | 15  | 19  | 27  |

| С           | Trace/Trace [mils]      | 3  | 4  | 5  | 9  | 12  | 15  | 19  | 27  |

| D           | Min. Trace Width [mils] | 3  | 4  | 5  | 9  | 11  | 14  | 17  | 25  |

According to those guidelines:

- The finished 35 µm Cu shall have DRCs for 18 µm base Cu;

- The finished 70 μm Cu shall have DRCs for 35 μm base Cu;

- The finished 105  $\mu m$  Cu shall have DRCs for 70  $\mu m$  base Cu. Proceed by analogy for all other thickness values.

The base Cu thickness of multilayer and single-sided PCB cores is identical to the finished value, since the cores are not plated. Example: an inner layer with 35  $\mu$ m Cu shall have the DRCs for 35  $\mu$ m Cu as shown in Table 6.

www.tspcb.pl

**Blind vias** (see Fig. 4 detail B) are made in multilayer PCBs only. The vias connect one of the outer PCB layers (top or bottom) with one or more inner layers, because blind vias are drilled to a defined non-through depth. The following processing restrictions apply:

- Minimum via diameter: 0,15 mm;

- The maximum depth (G) at hole diameters (D) **0.2**-**0.9 mm** is **0.23-0.75 mm**. The depth is calculated from the dependence G = 0.75 \* (D + 0.1) [mm];

- The maximum depth (G) is >1.00 mm for hole diameters

(D) >0.9 mm, as expressed by the formula G = D + 0.1

#### TECHNO-SERVICE

### 4.2. Minimum ring sizes and hole spacing

The list of minimum hole spacing and PCB mosaic details, and the minimum ring diameter values (see Fig. 4 detail E) is shown relative to the FR4 laminate circuit layer count in Table 7.

Table 7. Minimum ring sizes and PCB mosaic detail to hole distance for PCBs on the FR4 laminate

| No. of PCB layers                                          | 1; 2    | 4                 | 6                 | 8                 |

|------------------------------------------------------------|---------|-------------------|-------------------|-------------------|

| Min. ring size (hole dia. ≤5 mm)                           | std. 5  |                   |                   |                   |

| on outer layers [mils]                                     | min. 4  |                   |                   |                   |

| Min. ring size (hole dia. >5 mm) on outer layers<br>[mils] | 10      |                   |                   |                   |

| Rings on inner layers [mils]                               | N/A     | std. 5<br>min. 4* | std. 6<br>min. 5* | std. 7<br>min. 5* |

| Min hole/hole distance [mils]                              | 8       |                   |                   |                   |

| Min hole/pad distance [mils]                               | - 8 9 9 |                   |                   |                   |

| Min hole/path distance [mils]                              |         |                   | 9                 |                   |

\*Tear drops required as an additional Cu area at the pad to path connections

### 4.3. Aluminium based PCBs

MCPCBs on an aluminium base have different processing requirements:

- We manufacture single-sided non-plated MCPCBs only;

- Permissible Cu layer thickness: 35 μm, 70 μm, 105 μm;

- Permissible laminate thickness: 0.8-3.2 mm;

- Manufacturable coating types: Pb-free HAL (recommended), chemical gold plating;

The list of permissible component spacing on the aluminium core laminate PCBs is shown in Table 8.

Table 8. Minimum DRCs and ring width vs. Cu thickness

|                                                               | Cu foil thickness [µm] |    |     |  |

|---------------------------------------------------------------|------------------------|----|-----|--|

| Parameter                                                     | 35                     | 70 | 105 |  |

| Minimum spacing for pad/pad,<br>pad/path and path/path [mils] | 6                      | 9  | 12  |  |

| Min. path [mils]                                              | 5                      | 7  | 10  |  |

| Min. ring size [mils]                                         | 8                      |    |     |  |

The minimum hole diameter depends on the laminate thickness, as shown in Table 9

Table 9. Minimum hole diameter vs. laminate thickness

| Laminate thickness [mm] | Minimum diameter [mm] |  |  |

|-------------------------|-----------------------|--|--|

| 1.0                     | 0.8                   |  |  |

| 1.6                     | 0.9                   |  |  |

| 2.0                     | 1.00                  |  |  |

| 3.2                     | 1.60                  |  |  |

Aluminium PCB machining, and especially milling/routing, is one of the most time-consuming and cost-boosting processes. This is largely due to the high hardness of the laminate. We recommend scoring for square PCBs/panels to reduce the manufacturing costs.

## 5. PCB marking

On client request we can apply additional marks on our PCBs, e.g. UL compliance mark (for non-flammability certificates), production dates and other information. We place the markings in the design as ordered (and if specified) or in standard locations (if the location is undefined in the order), i.e. with the text features or on the top side soldermask according to our discretion. PCBs without soldermasks or text layers have the markings on the mosaic layer.

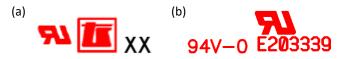

## 5.1. UL non-flammability certification

Our PCBs are marked according to the diagram presented in Fig. 6 with the mirror 'UR' (UR Recognised) logo and our TS logo. The location XX may feature the following marks: D, D1, D2, M, M1 or M2, depending on the laminate type used. The D-letter group is used to mark single- and double-sided PCBs. Multilayer PCBs carry the M-letter group. The digit (or the lack thereof) indicates the specific laminate group shown in the TS PCB Certificate. The PCB marking can also feature our Certificate No. **E203339** and the **UL94-V0** non-flammability class (see Fig. 6b).

39/ (3

Fig. 7. PCB production date coding

Fig. 6. (a) Typical and (b) extended UL-compliant PCB markings

Our UL certification allows us to mark all types of PCBs built on the following FR4 laminates TG max. = **150°C** and CTI = **PLC:3**. Recently we have been enabled to certify CTI 600V single- and double-sided laminates.

## 5.2. Date stamping

Date stamping is permanent marking of the PCB with its production date in the **week/year** format. An example of a PCB manufactured in week 39, year 2013 is shown in Fig. 7.

### 5.3. Other markings

Aside from the UL marks and date stamps, we offer permanent numbering of the PCBs in panels and of the panels. Moreover, we can place any optional marking the customer requires, provided that the custom mark meets the minimum Cu parameters or text line parameters, as explained in the previous sections. Table 10 below shows the symbols that Techno-Service may place on PCBs (which do not have to be specified in the design).

| Table 10. Typical optional markings for PCBs |     |                     |                  |              |                                |  |  |  |

|----------------------------------------------|-----|---------------------|------------------|--------------|--------------------------------|--|--|--|

| Тур                                          | е   | Techno-Service logo | <b>RoHS</b> mark | PB Free mark | Text                           |  |  |  |

| Symt                                         | ool | <b>ζ</b> , <b>Γ</b> | RoHS             | Ø            | Any string of basic characters |  |  |  |

## 6. List of abbreviations and symbols

- CTI (Comparative Tracking Index) the parameter defines the PCB's resistance to breakdown between paths in humid conditions. Expressed in volts [V].

- DRC (Design Rule Check) a process of design parameter verification (e.g. of geometrical dimensions) against the design criteria.

- mil \_\_\_\_ A unit of measure (equal to 1/1000 inch, i.e. 0.0254 mm) used as a raster basis in the design of PCBs.

- TC (Thermal Conductivity) a coefficient which represents the capacity of materials to conduct heat. Expressed in W/mK (watt per metre \* Kelvin).

- Tg (Glass Transition Temperature) the temperature of transition of a laminate from its glass (hard) form to a plastic (soft) form. Expressed in degrees Celsius (centigrade) [°C].