Ja, wir fertigen die Leiterplatten mit Lötpads für BGA und µBGA – Bestückung. Solche Leiterplatten müssen unbedingt mit chemisch Gold ausgeführt werden.

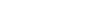

Der minimale Raster (Abb. 1, Entfernung bezeichnet als X) von solchen Baugruppen, möglich zur Fertigung in Techno-Service beträgt:

- für Vias 0,20 mm: 0,80 mm

In spezifischen Situationen (sehr einfache BGA, ohne Leiterbahnen zwischen Lötpads und Vias) ist es möglich einen kleineren Raster: 0,65 mm zu benutzen.

Ja – wir fertigen 2 Arten der durchkontaktierten Kanten:

Standard-Kanten-Durchkontaktierung

Die Durchkontaktierung deckt die Kante auf einem geraden Abschnitt – keine Bohrungen und Halbschlitzen auf der Kante. In diesem Fall wird die chemische Vergoldung empfohlen, aber es ist nicht nötig. Dennoch es lohnt sich die Vergoldung statt HAL bleifrei zu benutzen, um das Risiko von Rissbildung und Abblättern der Durchkontaktierung von Basismaterialkanten unter dem Einfluss von hohen Temperatur z.B. während der Bestückung.

Kanten-Durchkontaktierung mit Halbbohrungen oder Halbschlitzen

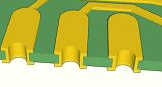

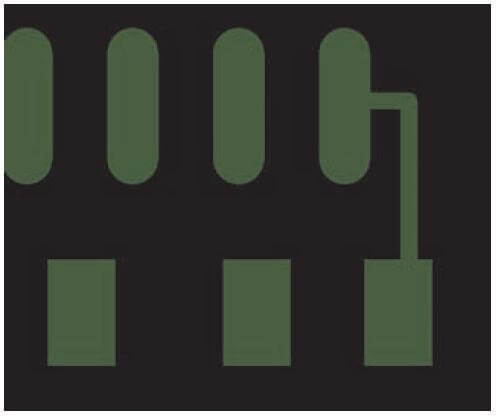

Auf der Leiterplattenkante befinden sich zusätzlich Halbbohrungen oder Halbschlitzen (Abb. 1).

Abb. 1. Beispiel von durchkontaktierte Halbbohrungen auf der Leiterplattenkante.

In diesem Fall ist die chemische Vergoldung notwendig, weil die Halbbohrungen und Halbschlitzen mehr anfälliger für Hitzschlag sind, der deren Beschädigung verursachen kann.

Bitte beachten Sie, dass der Rand der Platine, wo die Durchkontaktierung durchgeführt wird, muss gefräst werden – Ritzen kommt in dem Fall nicht in Frage.

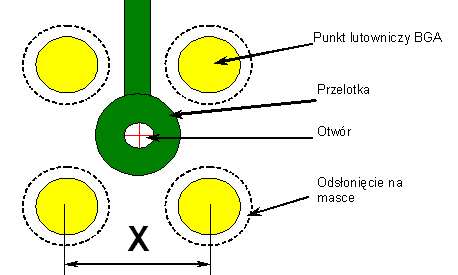

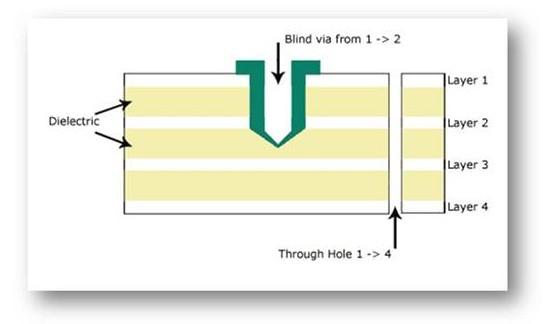

Burried Vias sind Löcher, die nur die inneren Cu-Schichten in Multilayer Leiteplatten miteinander verbinden. Diese Löcher gehen nicht durch die äußeren Schichten der Platine durch (siehe bitte Zeichnung unten).

Die Verwendung von burried Vias erhöht deutlich die Möglichkeiten des PCB-Entwurfsverfahrens, z.B. die Kupferfläche wird in den inneren Schichten viel effektiver genutzt. Die burried Vias-Technologie ermöglicht auch die Kosten der einzelnen PCB zu reduzieren, da die burried Vias nicht so großen Einfluss auf das Preis-Niveau haben wie z.B. die Erhöhung von Lagenanzahl oder der Abmässe einer Leiterplatte.

Um ein Projekt mit burried Vias korrekt zu erstellen, müssen solche Elemente berücksichtigt werden:

- maximale Durchmesser von burried Via: 1,5 mm,

- chemische Vergoldung von Pads auf Außenschichten ist notwendig,

- Technologie möglich nur für 4-Lagen Multilayer.

Auf die endgültige Dicke einer Leiterplatte haben verschiedene Elemente einen Einfluss:

- Dickentoleranz vom Basismaterial,

- Kupferdicke,

- Dicke der aufgetragenen Schichten (Lötstopplack, Durchkontaktierung, Beschichtung, Positionsdruck usw.) – Standard 0,17 mm.

Die Zusammenstellung von maximal zulässigen Dicken der fertigen ein- und doppelseitigen FR4 Leiterplatten (Gesamtdicken der Platinen) wurden unten in der Tabelle dargestellt.

| Basismaterialdicke [mm] | Basiskupferdicke [mm] | Maximal zulässigen Dicken der fertigen Leiterplatten [mm] | |

| Min. | Max. | ||

| 0,80 | 0,018 | 0,93 | 1,08 |

| 1,00 | Kupfer-Dicke eingerechnet in Basismaterialdicke | 1,10 | 1,19 |

| 1,20 | 1,30 | 1,45 | |

| 1,55 | 1,65 | 1,80 | |

| 2,00 | 2,07 | 2,27 | |

| 2,40 | 2,47 | 2,67 | |

| 3,20 | 3,24 | 3,50 | |

Die Oberfläche der Platinen wird immer vom Kunden bestimmt, dies ist jedoch nicht ganz beliebige Auswahl: bei der Entscheidung für eine bestimmte Oberfläche muss man die damit verbundenen Einschränkungen kennen. So ist Zinn billiger, aber gibt nicht so hochwertige Qualität wie Gold. Man kann es aber frei für weniger komplizierte Platinen wählen. Für schwierige Projekte ist Gold-Oberfläche immer eine bessere Alternative. In vielen Fällen besteht tatsächlich keine andere Wahl, da einige Platinen – aus technischen Gründen – einfach nicht verzinnt werden dürfen.

Chemisch Gold muss man also für solche Leiterplatten wählen, wo folgende Elemente verwendet wurden

- BGA-Bauteile,

- Leiterbahnabstand oder Leiterbahnbreite 100 um (4 mil),

- Pads gleich oder weniger als 200 um (8 mil) für einseitiges SMD,

- Pads gleich oder weniger als 300 um (1 mil) für doppelseitiges SMD,

- blind Vias,

- burried Vias,

- Dicke des Basismaterials weniger als 0,36 mm

- Schlitzen und halbdurchkontaktierte Bohrungen d.h. solche, die nur einerseits Pads haben,

- Halbbohrungen oder Halbschlitzen auf Leiterplattenkanten.

Es ist auch gut zu wissen, Gold-Oberfläche lohnt es sich nicht nur aus technischen Gründen zu wählen, aber auch, wenn die hohe Beständigkeit gegenüber Außen-Faktoren, perfekt glatte Pads-Oberfläche und exzellente Lötbarkeit von Bedeutung sind. Zudem kann man mit der Wahl dieser Oberfläche sicher sein, dass die Nickel-Schicht die Kupfer-Metallisierung vor der Auflösung bei der Montage schützt, die dennoch zum Gold angepasst werden muss, was bei der Projekt-Kalkulation berücksichtigt werden muss.

Chemisch Gold wird auch empfohlen, im Fall:

- Randverbinder – aufgrund der hohen Ebenheit,

- durchkontaktierte Kanten – das Risiko der Rissbildung und Abgehen der Durchkontaktierung von Kanten wird minimiert.

Um die Bohrungen in den Platinen richtig zu gestalten, muss man alle technologischen Einschränkungen berücksichtigen. In der Praxis bedeutet das, man darf nicht vergessen, die minimalen Bohrdurchmesser für eine bestimmte Materialdicke nicht zu überschreiten und bestimmte Padgrößen einzuhalten. Minimale Bohrdurchmesser wurden in der Tabelle angegeben:

|

Materialdicke [mm] |

Min. Bohrdurchmesser PTH nach der Durchkontaktierung [mm] |

|

1,55 |

0,15 |

|

2,00 |

0,20 |

|

2,40 |

0,20 |

|

2,50 |

0,25 |

|

3,00 |

0,30 |

Durchkontaktierte Bohrdurchmesser aufgrund der Auftragung der galvanischen Kupferschicht sind um etwa 0,1 mm kleiner gegenüber dem Durchmesser des Bohrers. Deshalb, um den Minimalwert für die NPTH-Bohrungen zu erhalten, sollte man zu den Durchmesser in der Tabelle 0,1 mm hinzuzufügen, z.B. für Basismaterial 1,55 mm beträgt die Mindest-NPTH-Bohrdurchmesser 0,30 mm.

Bitte beachten Sie auch, dass die Standard-Bohrdurchmessertoleranz für NPTH und PTH Bohrungen beträgt + 0,1 mm / – 0,05 mm. Wenn das Projekt spezifische Anforderungen für die Toleranz der Bohrdurchmesser enthält, sollte man dies deutlich in der Bestellung angegeben. Bitte beachten Sie, dass es keine Möglichkeit besteht, die Leiterplatten mit der Bohrdurchmessertoleranz von +/- 0,00 mm zu fertigen.

Im Multilayer-Leiterplatten-Bestellformular wird die Basislaminatdicke definiert, die solche Dicken umfasst: Kern(e) mit Kupfer 35 μm und der äußeren Kupferfolie 18 μm. Die maximale Toleranz der Endlaminatdicke beträgt ±10%. Für Standard Basismaterialdicke 1,55 mm kann man die Toleranz in Millimeter äußern, als 1,55 mm ±0,155, was bedeutet, dass die endgültige Dicke zwischen 1,395 mm bis 1,705 mm wird. Die Dickentoleranzen von Basismaterialien (Dickenbereich) werden durch solche Toleranzen verursacht:

- Dicken von Prepregs mit der Wert ±0,007 mm,

- Dicken von Kerne (siehe Tabelle 1.),

- Verfahren – in der Regel ±0,03 mm.

Tab. 1. Toleranzen von Kerndicken.

|

Kerndicke [mm] |

Toleranz [mm] |

|

0,10 |

±0,01 |

|

0,20 |

±0,02 |

|

0,36 |

±0,03 |

|

0,50 |

±0,04 |

|

0,71 |

±0,04 |

|

1,00 |

±0,06 |

Im Falle von Multilayer Leiterplatten mit dickeren Kupfer-Schichten (Cu 70 μm oder mehr) – erhöht sich die Dicke des Basismaterials. Für die Leiterplatte mit den Kernen mit Kupfer 70 μm wird die Dicke 1,62 mm (1,55 mm + 0,07 mm) betragen, da die Standarddicke um 35 μm Kupfer verdoppelt werden muss. Die endgültige Leiterplattendicke wird die Summe von Basismaterialdicke und im Prozess aufgetragenen Beschichtungen: galvanischen Kupfer und Lötstopplack. Die Dicken dieser Beschichtungen sind abhängig von der endgültigen Kupferdicke (Höhe), siehe Tabelle 2. Die höheren Mosaik-Schichten verursachen dickere Schichten, aus dem Grund des dickeren Lötstopplacks, um es dauerhaft zu machen, besonders an den Mosaik-Kanten. Neben der Tab. 2 wird die Art und Weise der Bestimmung der Standard-4-Layer-Leiterplattendicke und ihrer Toleranz dargestellt (http://www.tspcb.pl/centrum-wiedzy/do-pobrania/pobierz,263.html).

Tab. 2. Beschichtungsdicken.

|

End-Cu-Dicke [um] |

Beschichtungsdicken [mm] |

|

35 |

0,17 |

|

70 |

0,22 |

|

105 |

0,25 |

Der Standard-4 Layer-Lagenaufbau bestehend aus: – 4 x Prepreg-Typ 7628 – Dicke P = 0,72 ±0,028 mm, – Kern 0,71 mm / 35 μm -Dicke ±0,04 R = 0,78 mm. Deshalb beträgt die endgültige Dicke und ihre Toleranz P+R+0,03 mm (Prozesstoleranz) +0,17 mm (aufgetragene Beschichtungen) = 1,706 mm ±0,1. Um die Leiterplatte mit Standarddicke für dickere Kupferschichten zu erhalten, setzen Sie bitte diese Informationen in Feld „Kundenbemerkungen zur Leiterplattenfertigung” im Bestellformular ein. Diese Art von Informationen sollten auch bei ungewöhnlichen Basismaterialdicken und Toleranzen hinzugefügt werden.

- min. Abstände zwischen den leitfähigen Teilen,

- min. Leiterbahnbreiten,

- min. Bohrdurchmesser und Ring-Größen,

- min. Enthüllung auf dem Lötstopplack,

- Lagenzahl usw.

Die Analyse des Projekts ist in dieser Hinsicht eine Voraussetzung zur erfolgreichen Fertigung von Platinen. Allerdings sind alle Abweichungen von diesen Regeln leicht zu erkennen, da die meisten modernen Systemen zur PCB-Design die Funktion der Überprüfung und Korrektur solcher Fehler haben.

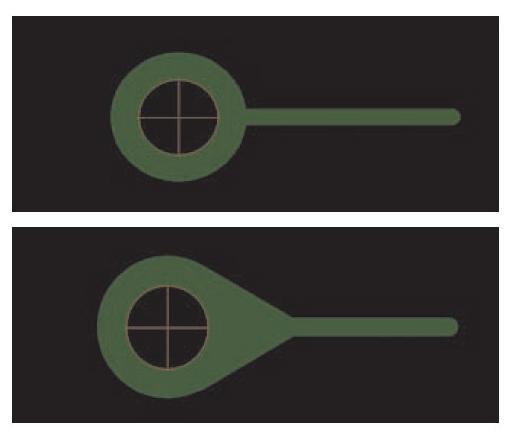

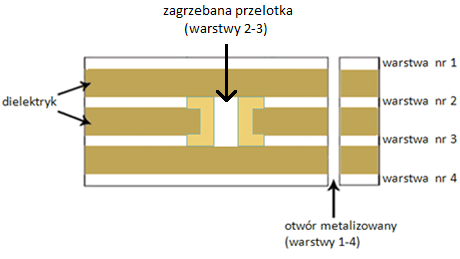

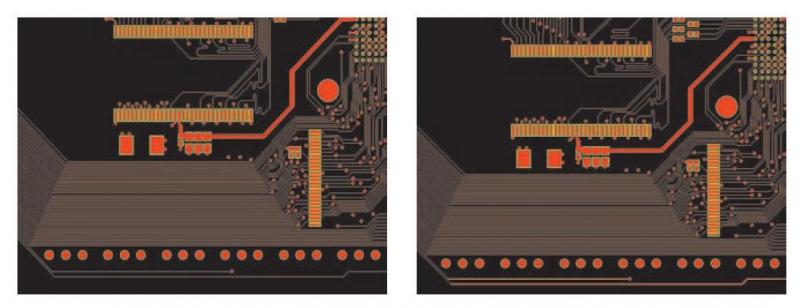

Abb. 1 Nicht empfohlene Lösung, solche Situation sollten vermieden werden, neben: eine gute Lösung –

Während der Herstellung treten oft Probleme auf, die aufgrund der Projekt-Lösungen entstehen, aber sind nicht das Ergebnis von Abweichungen von technologischen Bedingungen. Dies kann zur Verschlechterung der Qualität von Leiterplatten führen, deswegen werden im weiteren Teil dieses Artikels die Möglichkeiten ihrer Beseitigung dargestellt.

Abb. 2 eine schlechte Lösung, für beide untere Leiterbahnen besteht das Risiko des Durchätzens und mechanischer Beschädigungen. Neben: eine gute Lösung – Leiterbahnen mit der minimalen zulässigen Breite wurden aufgeweitet und das Risiko des Durchätzens und Leiterbahnenbeschädigung wurde stark reduziert.

Kupferoberfläche und Leiterbahnen

Eines der häufigsten Probleme ist unkorrekte Aufteilung der Kupferoberfläche auf Außenschichten. Die Effektivität des elektrochemischen Prozess der Kupferauftragung auf die Platinenoberfläche und innen der Bohrungen bleibt in enger Verbindung mit der Gleichmäßigkeit der Kupferverteilung auf der Platinenoberfläche.

Bereiche der Platine, wo eine niedrige Dichtung der Elemente ist (einzelne isolierte Leiterbahnen, Bohrungen), werden sich durch einen höheren Kupfer als andere Teile der Platine, die mehr Elemente oder große Flächen von Kupfer haben, aufzeichnen.

Die Anwendung einer solchen Lösung führt zu Problemen mit der Tolerranz der Bohrdurchmesser und der korrekten Lötstopplackauftragung auf Ränder der zu dicken Leiterbahnen an den Stellen, wo die geringe Dichtung der Elemente ist. Zur Verbesserung der Kuperverteilung wird empfohlen, eine zusätzliche Kupferoberfläche, die keine elektrische Funktion hat aber für die richtige Kupferverteilung im Prozess der elektrochemischen Durchkontaktierung sorgt, in Bereichen mit geringer Elementendichte hinzuzufügen.

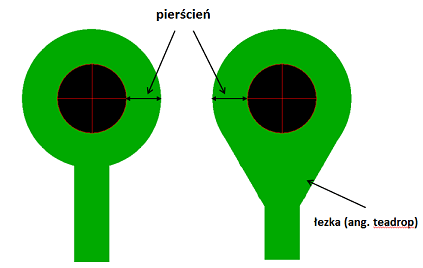

Abb. 3 Nicht korrekte Lösung für minimale zulässige Ringe und die richtige mit der hinzugefügten Träne.

Abb. 4 Zu kleiner Freiraum zwischen dem Pad und der Leiterbahn.

Abb. 5 Gute Lösung – korrekte Entfernung zwischen dem Pad und der Leiterbahn.

Die Abbildung 1 zeigt die Platine vor und nach der Zugabe von speziellen Kupfer–Füllungen. Ein weiteres Problem sind die minimalen Leiterbahnenbreiten. Die einzelnen isolierten Leiterbahnen mit der minimalen zulässigen Breite verursachen Probleme während des Ätzens der Leiterplatten.

Solche Leitebahnen sind leicht zu durchätzen, aber auch den mechanischen Beschädigungen und Offnungen ausgesetzt. Eine gute Regel beim Entwerfen ist die Reduzierung der Länge der Leiterbahnen mit einer minimalen Breite, d.h. man gibt die 6-Mil-Leiterbahn in den starkgepackten Bereichen , aber sobald die Dichte abnimmt, man kann die Leiterbahnbreiten um 2-3 Mil vergrößern – ein Beispiel davon zeigt die Abbildung 2.

Abbildung 3 zeigt die empfohlene Lösung. Eine weitere Ursache von Herstellungsfehlern oder Qualitätsproblemen der gefertigten Schaltungen ist der freie Raum zwischen dem Pfad und der Leiterbahn mit einer Breite von weniger als 5 Mil im Projekt.

Nach der Belichtung und Entwicklung des Photopolymers der 5-Mil oder kleinere Photopolymer-Streifen zeichnet sich durch eine begrenzte Haftung aus. Sehr oft trennt er sich ab und klebt an anderen Stellen der Platine. Die Folge davon sind Öffnungen oder Kurzschüsse je nach Technologie der Leiterplatten. Abbildung 4 zeigt das Problem und die Abbildung 5 die empfohlenen Lösungen.

Nutzung der Oberfläche

PCB-Designer haben auch einen Einfluss auf den Endpreis der Leiterplatten. Vor allem deswegen, dass die von denen eingesetzten Lösungen den Nutzungsbereich des Basismaterials ändern können. Da die Schaltungen nicht als Einzelstücke hergestellt werden, sondern in den Produktionsformaten (Beispielgröße des Formats 460 × 610 mm), empfehlen die Leiterplattenhersteller den Kunden vor dem Aufbau des Nutzens sie zu kontaktieren, um den optimalen Ausmaß des Nutzens zu bestimmen. Dies führt zu einer besseren Material-Ausnutzung.

Oft ist es so, dass Hinzufügen oder Wegnahme einer Platine im Nutzen reduziert stark die Produktionsabfälle des ungenutzten Basismaterial. Die oben dargestellten Probleme liegen vor allem auf die mechanischen und physikalisch-chemischen Eigenschaften der Materialien und Verfahren zur Herstellung der Leiterplatten.

Alle Tipps führen zur Erweiterung des Prozess-Fensters des Leiterplattenherstellers. Daher wird die Platine, die nach oben genannten Grundsätzen entworfen wurde, immer einfacher zu fertigen. Dies ermöglicht sie schneller, besser, günstiger und ohne das Risiko von Qualitätsproblemen zu produzieren.

Man kann keine Schlitze mit solcher Ausführung zu fertigen. Die gesamte Schlitze kann mit der Soldermaske bedeckt werden, oder gar nicht bedeckt sein (analog zu Vias). Normalerweise lassen wir die Schlitzen frei sein, also mit der metalisierten Ausführung der Oberfläche (chemisch Gold oder Hal bleifrei). Schlitzen, die mit der Soldermaske abgedeckt werden sollen, müssen klar durch den Kunden im Projekt markiert werden. Diese Regel gilt auch für Metalisierung der Leiterplattenkante.

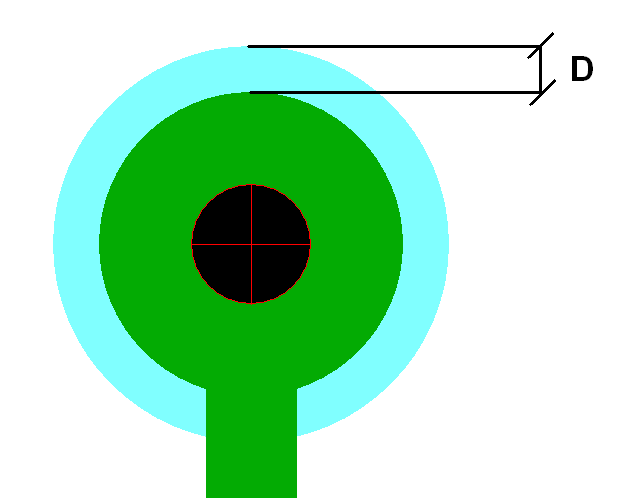

Alle Elemente, die verzinnt oder vergoldet sein sollen, müssen den Lötstopplack enthüllt haben und vergrößen um min. 6 mil in Bezug auf das Element auf der Mosaik. Anders gesagt – die minimale Enthüllung auf dem Lötstopplack beträgt 3 mil auf jeder Seite des Elements, was die Abb. 1 darstellt:

Abb. 1. Die Enthüllung des Pads auf dem Lötstopplack – D die Mindestenthüllung zur Seite.

Wir können PTH-Bohrungen mit einem Mindestdurchmesser von 0,20 mm zu fertigen. Der Mindestdurchmesser von NPTH-Bohrungen beträgt 0,30 mm. Es gibt jedoch keine Beschränkung für den maximalen Bohrdurchmesser. Die großen Bohrungen werden jedoch nicht gebohrt – die mit einem Durchmesser von mehr als 6 mm werden gefräst.

Der Standard–Fräsdurchmesser für mechanische Bearbeitung der Leiterplatten beträgt 2 mm.

Im Angebot haben wir auch Fräser mit anderen Durchmesser [mm]: 0,6; 0,8; 1.0; 1.2; 1,5; 2,0; 2.4.

Zusätzlich zu den Standard-Fräser haben wir auch Spezial-Fräser wie z.B. Kegel (30º, 60º), die unter anderem Abschrägung der Bohrränder oder Abschrägung der Steckverbinder ermöglichen, die nicht im Standardverfahren durchgeführt werden kann.

- einseitige auf Basismaterialien: FR4 (NPTH-Bohrungen / halb NPTH-Bohrungen), ALU (ohne Durchkontaktierung), Mikrowelle – Rogers (ohne Durchkontaktierung);

- doppelseitige auf Basismaterialien: FR4 (PTH-Bohrungen / NPTH-Bohrungen), ALU (NPTH-Bohrungen), Mikrowelle – Rogers (PTH-Bohrungen / NPTH-Bohrungen – hängt vom Basismaterial ab);

- multilayer Leiterplatten bis 8 Lagen auf FR4 Basimaterial (NPTH/PTH-Bohrungen).

Das dünnste, zum Ritzen mögliche Basismaterial hat die Dicke von 0,36 mm. Jedoch in dem Fall ist nur das Ritzen einerseits möglich (verwendet bei Basismaterialien mit einer Dicke von <0,5 mm). Wenn es beidseitiges Ritzen nötig ist, können wir es auf Basismaterialien mit einer Dicke ≥ 0,36 mm tun.

Die Toleranz der Ritz-Linie beträgt +/- 0,1 mm.

Die minimale Dicke des nicht geritzten Teils in Basismaterialien, die einerseits geritzt werden, beträgt 0,15 mm. Dies gilt für Basismaterialien mit einer Dicke von ≥ 0,5 mm und <0,8 mm. Angefangen von der Dicke von 0,8 mm bis zur Dicke von <2,4 mm lassen wir standardmäßig 0,3 mm des nicht geritzten Basismaterials. Bei Basismaterialien mit einer Dicke von 2,4 mm und mehr entspricht der nicht geritzte Teil von 20% der Basimaterialdicke.

Alle Parameter beziehen sich auf das Basismaterial, d.h. solches, das noch nicht zur Produktion verwendet wurde.

Die Leiterplatten mit blind vias haben zusätzliche Bohrungen, die bestimmte Lagen in der Multilayer Leiterplatte miteinander verbinden. Solche Bohrungen werden nicht ganz durchgebohrt und daher kommt ihr Name – blind vias. Durch Bohren der Bohrungen bis zur Tiefe, auf der sich eine Kupferschicht innerhalb der Leiterplatte befindet, kann – nach der Durchkontaktierung – eine elektrische Verbindung zwischen den ausgewählten Lagen erzielt werden. Dies erhöht deutlich die Möglichkeiten der Leiterplatten und deren Anwendungen. Das Schema einer solchen Platine wird in der folgenden Abbildung dargestellt:

Bei der Vorbereitung eines Projekts mit blind vias sind zwei Punkte zu beachten:

vor allem müssen die Platinen mit blind vias vergoldet werden (sie dürfen nicht verzinnt werden!)

sowie darf die maximale Tiefe der blind vias 75 % des Bohrer-Durchmessers nicht überschreiten, mit dem es gebohrt wird.

Zum Beispiel darf die Tiefe der blind vias im Durchmesser für den Bohrer 0,4 mm maximal 0,3 mm betragen. So gestaltete Leiterplatten können in unserem Betrieb erfolgreich hergestellt werden – es bestehen keine sonstigen Einschränkungen in dieser Hinsicht.

Die minimale Padgröße (AR – Annular Ring ) hängt von der Lagenanzahl und Lagentyp (äußere/innere) ab, auf der sich Pad befindet.

Für die Außenlagen (unabhängig von der Leiterpllatenart) beträgt die minimale Padgröße immer:

- 0,125 mm (5 mil) für FR4-Basismaterialien,

- 0,20 mm (8 mil) für ALU-Leiterplatten.

Die folgende Abbildung zeigt, wie die Breite des Rings gemessen wird – es ist die Hälfte der Differenz des Pads- und Bohrdurchmessers, das sich in diesem Pad befindet. Auf der Abbildung wurde auch Pad mit einer Träne zum Vergleich gezeigt.

.png)

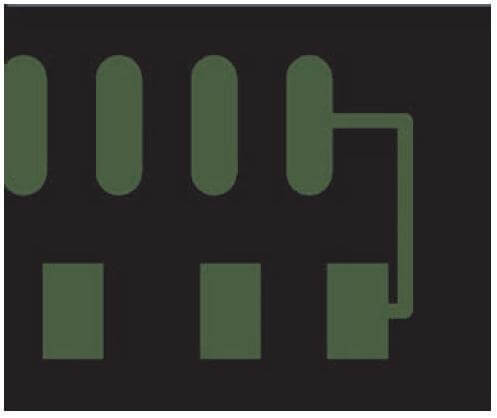

Wir fertigen vier Arten von Vias:

1. Vias – Durchkontaktierungen, die mit dem Lötstopplack abgedeckt werden. Diese Vias sind in der Regel nicht verstopft (plugged), der Lötstoplack wird im Vorhang-Giessverfahren darauf aufgetragen und deckt somit die Kanten und Ränder der Löcher.

2. Plugged and covered Via – standard – Vias werden mit einem speziellen photochemisch gehärteten Lack verstopft, vor der Lötstopplack-Verfahren. Die Vias sind 100% plugged und mit dem Lötstopplack abgedeckt. Mit dieser Methode beträgt der Füllungsgrad von Via mit Lötstopplack etwa 40%. Die Füllungsfarbe gewährleistet optimales Anhalten des Lötes vor dem Eintritt auf die andere Seite der Leiterplatte, jedoch ist die Oberfläche von Vias nicht flach. Dieses Verfahren kann bei Zustopfung von Vias mit der Ausführung in HAL bleifrei oder ENIG mit Endkupfer 35µm verwendet werden. Diese Art von Vias eignet sich für Verstopfen von Bohrdurchmesser von max. 0,6mm.

3. Plugged and covered Via – flat – Um weitere Ebenheit von Via und eine Erhöhung der Füllungsgrad von Vias mit dem Lack zu erhalten, verwenden wir das Verfahren des Zustopfen, wo der Füllungsgrad > 80% beträgt. Die Anwendung dieses Verfahren erfordert die Ausführung der Leiterplatten in ENIG – Technologie, die Ausführung in HAL bleifrei ist in dem Fall nicht möglich. Dieses Verfahren kann auch bei Zustopfung von Vias in Leiterplatten mit Endkupfer 70µm verwendet werden. Diese Art von Vias eignet sich ähnlich wie o.g. für Verstopfen von Bohrdurchmesser von max. 0,6mm.

Dieses Verfahren kann auch zum Verstopfen von Vias in Pads verwendet werden, jedoch ist der Vias-Verstopfen-Lack nicht mit Kupfer bedeckt und um das Loch heurum bleibt 3-Mil-Hülle aus diesem Lack. Bei der Bestellung dieser Art von Vias sollte man eine Anmerkung „FLAT VIAS” hinzugefügen.

4. Plugged Via – Durchkontaktierungen, die nach der Ausführung der Oberfläche (ENIG, HAL bleifrei) mit einem speziellen, termisch-gehärteten Lack, aufgetragen im Siebdruck-Verfahren, verstopfen werden. Die Vias sind verstopft, jedoch zeichnen sich durch Unebenheit aus. Der Lack geht deutlich über die Kupfer-Oberfläche hinaus. Diese Art von Vias eignet sich für Verstopfen von Bohrdurchmesser von max. 1mm.

Während der Vorbereitung des Entwurfs sind die Beschränkungen zum Durchmesser von plugged Via zu berücksichtigen. Im Fall von Via mit einem Durchmesser von 0,5mm kann der beliebige Art von Via ausgewählt werden. Im Fall von Via mit einem Bohrdurchmesser z.B. von 0,8mm können wir nur plugged Vias verwenden.

Die Mindestmenge des Löttstopplacks an der Kante der Leiterbahn beträgt 7 μm, unabhängig von der Endkupferdicke.

Die Menge des Löttstopplacks an den Massen:

– 50 μm für Enkupfer 35 μm

– 85 μm für Endkupfer 70 um

– 120 μm für Endkupfer 105 um.Die anderen Dicken des Löttstopplacks sollten individuell bei der Bestellung abgesprochen werden.

Bei der Entwicklung einer Leiterplatte darf man nicht vergessen, die entsprechenden Abstände der leitfähigen Teilen von der Fräslinie zu beachten, es schützt die Platinen von der Gefahr eines elektrischen Durchschlags im Gehäuse oder in anderen Elementen am Rande der Leiterplatte. So gewährleistet die Einhaltung eines korrekten Abstands eine entsprechende Isolierung der leitfähigen Elemente der Platine.

Um den Abstand korrekt zu bestimmen, sollte man die minimalen Werte nicht vergessen, die jeweils betragen:

a) Mindestabstand der Masse vom Rand der Leiterplatte (Fräslinie) beträgt 0,20 mm (8 mil)

b) Mindestabstand der Leiterbahn vom Rand der Leiterplatte (Fräslinie) beträgt 0,25 mm (10 mil)

c) Mindestabstand der Masse, der Leiterbahn und des Pads vom Rand der Leiterplatte beträgt in inneren Schichten 0,20 mm (8 mil).

Den Mindestabstand der Massen und Leiterbahnen von der Ritzlinie, abhängig von der Materialdicke, bestimmt die folgende Tabelle:

|

Materialdicke |

0,55 mm |

0,8 mm |

1,0 mm |

1,2 mm |

1,55 mm |

2,0 mm |

2,4 mm |

|

Min. Abstand der Ritzlinie von Massen |

0,3 mm |

0,42 mm |

0,52 mm |

0,62 mm |

0,8 mm |

1,04 mm |

1,24 mm |

|

Min. Abstand der Ritzlinie von Leiterbahnen |

0,15 mm |

0,21 mm |

0,26 mm |

0,31 mm |

0,4 mm |

0,52 mm |

0,62 mm |