Testowanie PCB. Testowanie palcowe – optymalizacja czasu testowania

Pomimo zastosowania szybkiej mechaniki i usprawniania sekwencji przemieszczania głowic pomiarowych gwarantujących przetestowanie nawet kilku tysięcy punktów testowych na minutę, czas testu pojedynczego formatu produkcyjnego zawierającego skomplikowane i upakowane obwody HDI może dochodzić do kilkunastu minut lub nawet więcej. Długi czas testu staje się zasadniczym ograniczeniem testerów palcowych, także w przypadku obwodów o niewielkich rozmiarach, mogących wystąpić na pojedynczym formacie w ilości kilkuset sztuk. Aby zredukować czas testowania wielu producentów proponuje swoje własne autorskie optymalizacyjne rozwiązania sprzętowe i programowe. Przykładowe techniki optymalizacyjne zostaną omówione na bazie rozwiązań firmy Gardien – światowego dostawcy urządzeń i rozwiązań technologicznych w dziedzinie testowania obwodów drukowanych.

Jedną z metod redukcji czasu testowania jest zastosowanie wstępnego testu pojemnościowego, poprzedzającego test rezystancyjny.

Test pojemnościowy polega on na obliczeniu pojemności sieci elektrycznych na podstawie projektu i porównywaniu ich we wszystkich rzeczywistych obwodach znajdujących się na formacie produkcyjnym.

O możliwości użycia testu pojemnościowego oraz doborze sieci decyduje oprogramowanie, które analizuje rozkład mozaik w badanym obwodzie. Podstawowym kryterium zastosowania testu pojemnościowego jest obecność w mozaikach obszarów referencyjnych o dużym wypełnieniu miedzią, względem których możliwe jest określenie pojemności sieci położonych na pozostałych warstwach. Podstawową zaletą tego testu jest znaczne skrócenie procedury pomiarowej, ponieważ jedna lub dwie sondy stale dotykają punktów testowych warstwy sieci referencyjnej, a pozostałe sondy badają pojemność pozostałych sieci, za pomocą pojedynczego dotknięcia sondy.

W przypadku wykrycia znacznego odchylenia pojemności sieci w jednym z obwodów na formacie produkcyjnym następuje automatyczne przełączenie trybu testowania do testu rezystancyjnego, w celu dokładnej weryfikacji sieci tego obwodu.

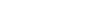

Inną ciekawą koncepcję zastosowano w testerze Acceler8 firmy Gardien (rys. 1a), wykorzystywanym w TS PCB. Polega ona na wykonaniu zgrubnego testu wstępnego na specjalnym testerze, w którym głowica pomiarowa składa się z układu 4096 sond i jest wykonana w formie dywanu z delikatnych miedzianych włosków rozmieszczonych ze stałym rastrem (rys. 1b).

(a)

(b)

Rys. 1. Tester Acceler8 (a) oraz widok jednego z modułów jego głowicy pomiarowej uzbrojonego w sondy (b).

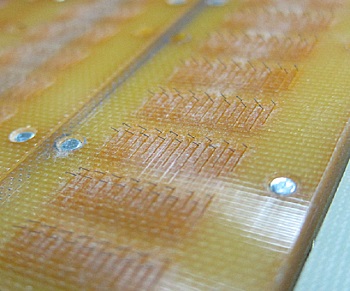

Przed rozpoczęciem testu konieczne jest pełne przetestowanie pojedynczego formatu produkcyjnego na testerze palcowym w celu zebrania wektora danych uczących dla Acceler8, na którego bazie oprogramowanie wyznacza jakie sondy głowicy będzie można wykorzystać z uwzględnienie rozkładu punktów testowych na formacie. Następnie kolejne formaty kierowane są już na tester Acceler8, gdzie podczas procedury pomiarowej omiatane są włoskami sond z jednej, a po przełożeniu, z drugiej strony. Na podstawie zebranych danych wyznaczane są wyniki testu ciągłości i izolacji. Dla każdego formatu oprogramowanie analizuje wyniki pomiarów i określa ile procent sieci zostało przetestetowanych oraz generuje skrócony program testu uzupełniającego dla pozostałych sieci na tester palcowy.

W zależności od układu mozaik uzyskuje się w ten sposób łączne skrócenie czasu testowania od 30% do ponad 50%. Ze względu na wydłużony proces nauki testera Acceler8, zysk czasu testu widoczny jest już od kilku formatów produkcyjnych.

Oferowany przez testery palcowe czas testu jest akceptowalny przede wszystkim w produkcji prototypowej i małoseryjnej. Takiemu wykorzystaniu sprzyja także niski koszt uruchomienia, ponieważ przygotowanie procedury testowej odbywa się wyłącznie w sferze programowej, poprzez przygotowanie programu do testowania i nie wymaga dodatkowych inwestycji sprzętowych.

.jpg)

.jpg)