Testowanie PCB. Klasyfikacja metod testowania obwodów oraz wprowadzenie do testowania elektrycznego

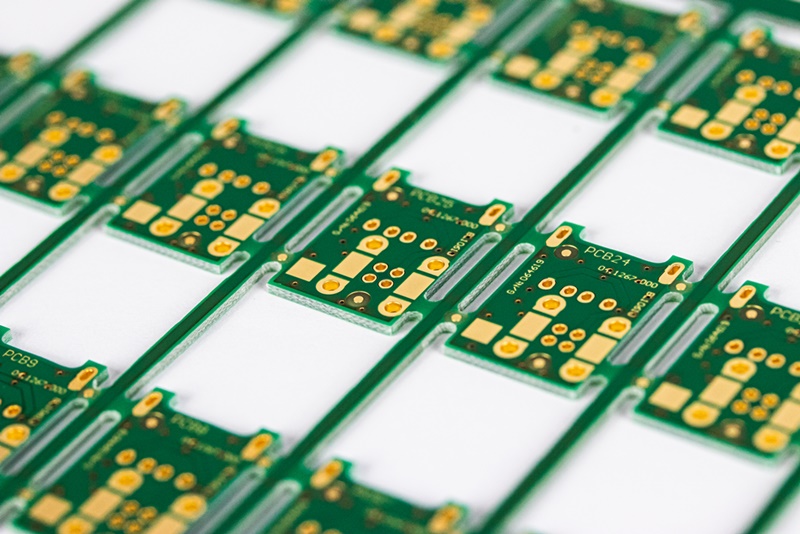

Produkcja obwodów drukowanych, charakteryzuje się określonym poziomem egzemplarzy wybrakowanych. Jako obwód wybrakowany rozumie się każdy egzemplarz niespełniający założeń projektowych klienta, a także ściśle określonych norm branżowych. Przykładem takiej normy, stosowanej przez renomowanych producentów PCB, w tym TS PCB, jest IPC-600H. Ten oraz inne standardy klasyfikują dopuszczalny zakres defektów wykonania poszczególnych warstw obwodu, w tym mozaik. O ile występowanie drobnych uchybień w odwzorowaniu kształtów mozaiki jest dopuszczalne, o tyle musi zostać zachowana pełna zgodność struktury i liczby odwzorowanych sieci elektrycznych z projektem .

Celem wykonywanego u producenta PCB testowania obwodów drukowanych (ang. bare board testing) jest sprawdzenie, czy spełniają one wytyczne klientów i normy branżowe, a w szczególności, czy sieci elektryczne w wyprodukowanych obwodach są w pełni zgodne z dokumentacją projektową.

SYSTEMATYKA TESTOWANIA

Klasyfikację metod testowania warstw przewodzących PCB przedstawiono na rys. 1. Upowszechniły się dwa główne kierunki rozwojowe: testowanie elektryczne (ang. electrical testing, e-test), podczas którego weryfikowana jest struktura sieci rzeczywistego obwodu względem jego projektu oraz testowanie optyczne (ang. Automated Optical Inspection, AOI), bazujące na graficznym porównaniu obrazów mozaik obwodu z wzorcowymi obrazami wygenerowanym z dokumentacji projektowej.

Rys. 1. Klasyfikacja metod testowania PCB.

W testowaniu elektrycznym wyróżnia sie dwie techniki dostępu sond pomiarowych do punktów testowych mozaik obwodu, poprzez: testery z ruchomymi sondami pomiarowymi (ang. flying probe testers) oraz testery ostrzowe, w których nieruchome sondy występują w postaci igieł o średnicach i rozmieszczeniu dopasowanym do rozmiaru i położenia pól kontaktowych testowanego obwodu (ang. fixed probe testers, bed of nail testers).

TESTOWANIE ELEKTRYCZNE

Test elektryczny wykorzystuje fakt, że lista sieci elektrycznych obwodu, określana z angielskiego jako netlist, stanowi sygnaturę charakterystyczną dla każdego obwodu. Najczęściej spotykanymi defektami mozaik, które modyfikują netlistę, są uszkodzenia katastroficzne w postaci zwarć (ang. shorts) pomiędzy różnymi sieciami oraz rozwarć (ang. opens). Zwarcia takie redukują liczbę sieci, natomiast rozwarcia mogą generować nowe dodatkowe sieci. Znacznym ułatwieniem testowania elektrycznego jest duża dostępność węzłów sieci, ponieważ każdy z nich jest punktem testowym, do którego można podłączyć aparaturę pomiarową testera.

Weryfikowanie netlisty wykonywane jest drogą dwóch testów rezystancyjnych: ciągłości (ang. continuity test) oraz izolacji (ang. isolation test). Podczas obu testów badana jest rezystancja, przy czym dla testu ciągłości – pomiędzy punktami testowymi w obrębie jednej sieci, a dla testu izolacji – pomiędzy daną siecią i punktami innych sąsiednich sieci elektrycznych (ang. adjacent nets).

Zasady testu rezystancyjnego, a w szczególności klasyfikacji wyników pomiarów rezystancji definiuje norma IPC9252. Wg niej rezystancja pomiędzy punktami testowymi o wartościach do 10 Ω świadczy o ich zwarciu, co oznacza, że punkty przynależą do tej samej sieci. Pomiar jest interpretowany jako rozwarcie w przypadku uzyskania rezystancji rzędu 10 MΩ i więcej. Obszar pomiarowy pomiędzy punktami 10 Ω oraz 10 MΩ oznacza występowanie upływności pomiędzy punktami testowymi i ze względu na niejednoznaczność interpretacji jest przez tester wykrywane jako błędny pomiar.

Tego typu błędy mogą powstawać wskutek niedokładnego kontaktu sond pomiarowych z powierzchnią punktów testowych spowodowanego np. zabrudzeniem lub uszkodzeniem sond. Defekty te wymagają dodatkowej weryfikacji poprzez ponowny test po oczyszczeniu powierzchni kontaktowych lub przy wykorzystaniu stacji napraw PCB (ang. fault station), która ułatwia ponadto określenie miejsc izolacji lub zwarć sieci na podstawie logów testera.

.jpg)

.jpg)