Testing printed circuits: Classification of the circuits testing methods and introduction to electrical testing

Printed circuits production similar to a serial production of other goods is characterized with a certain efficiency level or the level of the rejected pieces. Rejected circuit means each piece which is not fulfilling design assumptions of the customer or precisely specified industry standards. An example of such standard, used by PCB renowned producers, including TS PCB, is IPC-600H. This and other standards classify and specify allowed defects range of the individual circuit layers making, including the mosaics. As long as presence of small faults in the mosaic shape representation is allowed as full compliance of the structure and the number of represented electrical nets with the design must be maintained.

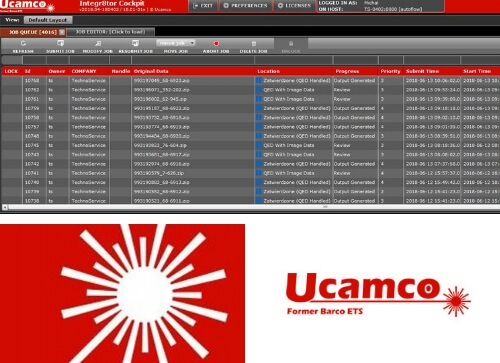

The purpose of performed at the PCB producer testing of the printed circuits (bare board testing) is checking if they are fulfilling the customers’ and industry standards requirements and especially if the electrical nets in produced circuits fully comply with the design documentation. Due to a complexity of topic the article was divided into a few parts in which the testing systematic and the most popular methods and technics of testing printed boards mosaics together with the characteristic features and restrictions will be discussed.

Testing systematics

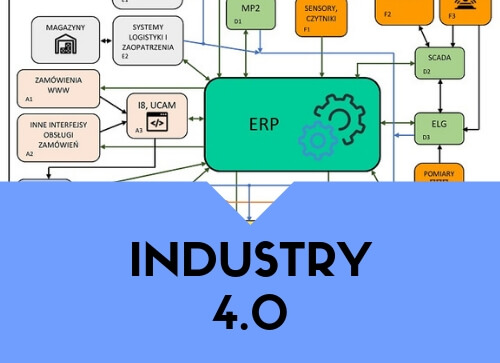

Classification of the testing methods of the PCB conductive layers was presented on pic. 1. Two main development directions have spread: electrical testing (e-test), during which the net structure of the real circuit in relation to it design is verified and optical testing (Automated Optical Inspection, AOI) basing on graphical comparison of the circuit mosaics compared with the exemplary images generated from the design documentation.

Pic. 1. PCB testing methods classification.

In the electrical testing the two technics are distinguished of the measuring probes access to testing points of the circuit mosaics, by: testers with the moving testing probes (flying probe testers) and blade testers in which stationary probes are present in a form of nails of diameters and distribution suited to the dimension and location of the contact fields of the tested circuit (fixed probe testers, bed of nail testers).

Electrical testing

The electrical test uses the fact that the list of the electrical nets of the circuit, called netlist, is a characteristic signature for each circuit. The most often met mosaics defects, which modify the netlist, are catastrophic damages in a form of short-circuits (shorts) between different nets and open-circuits (opens). Such shorts reduce the nets number and the opens can generate new additional nets. Significant simplification of the electrical testing is a big number of available net nods, because each one of them is a testing point to which you can connect the tester measuring equipment.

Verifying the netlist is performed by two resistance tests: continuity (continuity test) and isolation (isolation test). During both tests the resistance is examined whereas for the continuity test – between the test points in one net, and for the isolation test – between given net and the points of other neighboring electrical nets (adjacent nets).

The resistance test rules, and the resistance measurement results classification especially are defined in IPC9252 standard. According to this standard the resistance between test points of value up to 10 Ω means it shortening which means that points belong to the same net. The measurement is interpreted as an open-circuit in case of achieving the resistance of 10 MΩ and more. Measurement range between points 10 Ω and 10 MΩ means presence of the leakage between test points and due to the interpretation ambiguity is detected by the tester as a wrong measurement.

Those type of errors can be created due to an inaccurate measuring probes contact with the test points surface caused by e.g. dirt or the probes damage. Those defects require additional verification by performing the test again after cleaning the contact surfaces or using PCB repairs station (fault station) which moreover will ease specifying the net isolation or the net shorts places basing on the tester logs.